- Simplified RISC CPU design

Let's discuss the simplified RISC CPU design.

2. RISC CPU structure

4 arithmetic operator

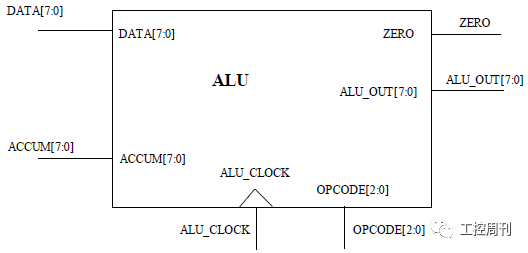

The arithmetic logic operation unit realizes 8 basic operation operations such as addition, AND, XOR, and jump according to the input 8 different operation codes. A variety of other operations, as well as logical decisions, can be implemented using these basic operations.

The VerilogHDL program is shown in the following module:

//------------------------------------------

Module alu (alu_out, zero, data, accum, alu_clk, opcode);

Output [7:0]alu_out;

Output zero;

Input [7:0] data, accum;

Input [2:0] opcode;

Input alu_clk;

Reg [7:0] alu_out;

Parameter HLT = 3'b000,

SKZ = 3'b001,

ADD = 3'b010,

ANDD = 3'b011,

XORR = 3'b100,

LDA = 3'b101,

STO = 3'b110,

JMP = 3'b111;

Assign zero = !accum;

Always @(posedgealu_clk)

Begin //Operation code comes from the lower 3 bits of the output opc_iaddr<15..0> of the instruction register

Casex (opcode)

HLT: alu_out<=accum;

SKZ: alu_out<=accum;

ADD: alu_out<=data+accum;

ANDD: alu_out<=data&accum;

XORR: alu_out<=data^accum;

LDA: alu_out<=data;

STO: alu_out<=accum;

JMP: alu_out<=accum;

Default: alu_out<=8'bxxxx_xxxx;

Endcase

End

Endmodule

//------------------------------------------

BLDC Gear Motor

Biotept supply high quality DC Planetary gear motor,

22mm planetary reducer gearbox

28mm planetary reducer gearbox

32mm planetary reducer gearbox

36mm planetary reducer gearbox

42mm planetary reducer gearbox

56mm planetary reducer gearbox

600mm planetary reducer gearbox

small size dc gear motor with low speed and big torque

suitable to small diameter, low noise and big torque application

reduction ratio: 3.7, 4, 5.2, 14,19,27,51,71,100,139,189,264,369,516,720

Bldc Gear Motor,Bldc Gearbox,Bldc Motor With Gearbox,Brushless Dc Gear Motor,Sliding Gate Motor

Ningbo Biote Mechanical Electrical Co.,Ltd , https://www.biotept.com